|

自2002年以来,Impluse公司为数以百计的设计团队解决了问题。一路走来,我们已经建立了框架,沙盒和参考算法来提供模板给我们半定制设计。我们取得您的规范说明,并从已知的良好的模块中构建一个快速原型。这使你能够快速地测试你的想法并缩短你的日程表。模块有良好的文档记录,大多数都有完整的VHDL测试套件,并在最终的应用程序中构建良好。查看下面的IP块的部分列表,或者教程、视频和文章,并使用联系表单来让我们知道如何帮助您的设计。Impluse公司可以在一个项目或公司范围内提供有效的解决方案。 |

|

|

摄像头通信接口

许多以太网照相机都将使用于GigE Vision和GeniCam协议。软件API和以太网协议创建了一个层,使这些模块能够从FPGA到FPGA支持的开发板的范围进行交叉编译。ARM处理器也可以加入。Impluse公司在这方面有越来越多的模块。Windows (Intel CPU) 或者Linux是标准。Impluse可以帮助建立链接到ARM,NIOS,Microblaze或者其他模块。以及为您的独有应用程序的定制服务。UDP以太网协议使数据能够很容易地流到FPGA逻辑。可以使用空闲的FPGA处理器来处理协议。Impluse公司有很多这样的构建模块,并对其作为一个扩展领域感兴趣。 |

|

|

图像卷积或重建

比如这个后投影算法在一半的时间里被开发出来,并且更重要的是,若其使用HDL进行设计可在1/8的时间里进行迭代。在这个设计中,一个256通道的CAT扫描仪图像是在一个单独的FPGA中被调和。这种设计是可用的,通常只需要花费4周的时间就可以根据您的规范进行修改。 |

|

|

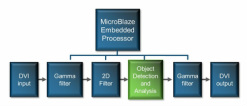

目标捕捉

使用一个嵌入式处理器,将能迅速地设置一个片上系统,在高清视频流中识别一个对象的三算法系统,“聚光灯”的物体和平滑的跟踪。在我们的一个示例中,对象定义是在几行C代码中捕获的,并可以在几分钟内进行更改。 |

|

|

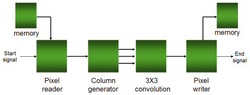

图像滤波器

图像滤波器快速修改和试验。这个特殊的设计利用了可选的板载的软微处理器。它还通过使用针对FPGA开发板的Impluse平台支持包中的C控制来定位到内存。对卷积或其他滤波器的更改就像更改一行代码一样简单。 |

|

|

可编程网络低延迟原型“沙盘”

Impulse提供我们可以为UDP连接、低延迟交易模块、线速度过滤器模块等提供UDP。我们可以提供UDP到UDP连接、低延迟交互模块、线速度滤波器模块等等。有了这个集成的开发环境,您的团队可以快速地将滤波器、私有商用逻辑以及其他的业务转移到以太网,并在短时间内进行试验交易系统可以在微秒级的延迟下运行。这个特定的开发系统是基于Solarflare的应用卸载引擎(AOE),并包含8个小时的培训。

更多扩展文档可以参阅:http://www.impulseaccelerated.com/Solarflare/ |

|

|

位流接口

在一定范围的项目内易于构建的位流接口,允许独立进程作为模块来被创建和添加。位流在FPGA组织中传播,创建强大的多位流进程加速系统以计算边界进程。 |

|

|

金融系统

用于遵从,交易或者冒险。交易系统可以在微秒级的延迟下运行。分析学可以在50X倍甚至更快的速度下运行。遵从或者冒险检查可以被并行插入到交易逻辑中,以将交易时间的影响最小化。更重要的是,解决方案是模块化的,基于HLL的,以及可用户自定义的。这降低了所有权的长期成本,并使它们能够更快地迁移到新的平台上。 |

|

|

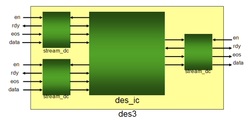

加密器和解密器

如3DES,在HLL中实现是及其快速的。在Impulse的“壳(shell)”是DES,3DES,河豚算法或者其他加密引擎的例子。甚至更有用的是将加密算法与低延迟框架结合起来,比如UDP或金融类型模型(在此页的其他地方列出)。 |

|

|

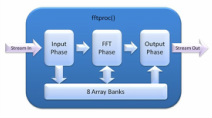

2-4基数FFT(或自定义FFT)

Impluse公司提供了一种现场迭代的4次幂FFT,其使用了2个基数为4的蝴蝶算法和8根内存条。流水线和内存条访问索引允许吞吐量翻了一倍,对比于单一的基数4的算法。双极FFTs和许多定制值FFTs也可以在几周内获得。 |

|

|

平台支持包(PSPs)

Impluse提供C级别的支持给嵌入式处理器和完整的基于FPGA的开发板。这允许您很容易地使用C语言写入存储器,I/O,总线和其他您的系统的特点。然后PSP会创建需要用来驱动特定硬件的HDL代码。针对您拥有的硬件的自定义PSPs是允许的。 |